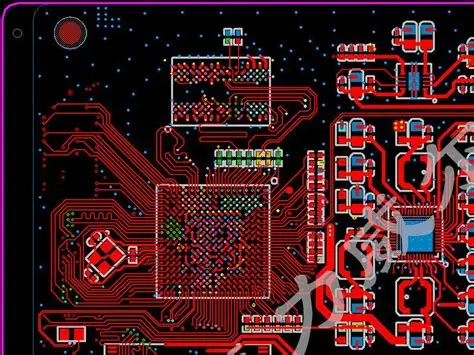

Durante il layout della scheda, come possiamo garantire un funzionamento efficiente della memoria flash e di altri componenti programmabili?

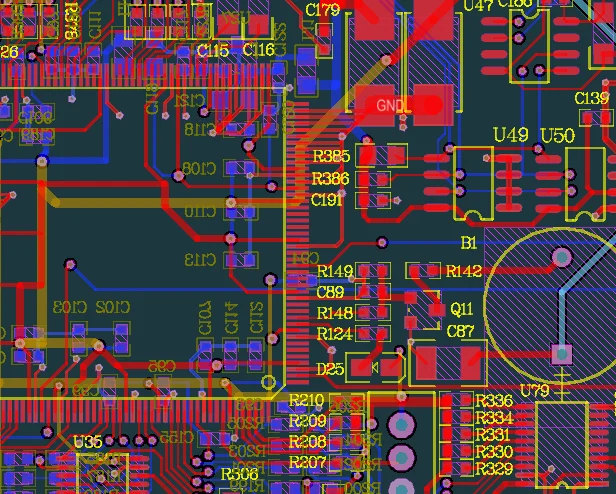

La programmazione della memoria flash può talvolta richiedere molto tempo (fino a 1 minuto per memorie o banchi di memoria di grandi dimensioni). Pertanto, è necessario impedire l'inversione di polarità da parte di altri componenti durante questo periodo, poiché potrebbe danneggiare la memoria flash. Per evitare ciò, tutti i componenti collegati alle linee di controllo del bus indirizzi devono essere impostati in uno stato di alta impedenza. Analogamente, anche il bus dati deve essere in grado di essere isolato per garantire che la memoria flash sia scarica e pronta per la successiva programmazione.

I componenti programmabili in-system (ISP), come quelli di Altera, Xilinx e Lattice, hanno requisiti specifici, oltre ad altre considerazioni particolari. Oltre a garantire i prerequisiti di testabilità meccanica ed elettrica, è necessario garantire la capacità di programmazione e verifica dei dati. Per i componenti Altera e Xilinx, viene utilizzato il formato Serial Vector Format (SVF), che si è recentemente evoluto in uno standard quasi industriale. Molti sistemi di test possono programmare tali dispositivi e utilizzare i dati di input all'interno dell'SVF per generare segnali di test.

Anche la programmazione di questi dispositivi tramite la Boundary Scan Chain (JTAG) utilizza il formato dati seriale. Durante la compilazione dei dati di programmazione, è fondamentale considerare l'intera catena di dispositivi all'interno del circuito; i dati non devono essere ridotti al solo dispositivo da programmare. Durante la programmazione, il generatore automatico di segnali di test tiene conto dell'intera catena di componenti e incorpora altri componenti in un modello di bypass.

Al contrario, Lattice richiede dati in formato JEDEC ed esegue la programmazione parallela tramite porte di input e output standard. Dopo la programmazione, i dati vengono utilizzati anche per verificare la funzionalità dei componenti. I dati forniti dal reparto di sviluppo devono essere il più facilmente utilizzabili dal sistema di test direttamente, o con una conversione minima.

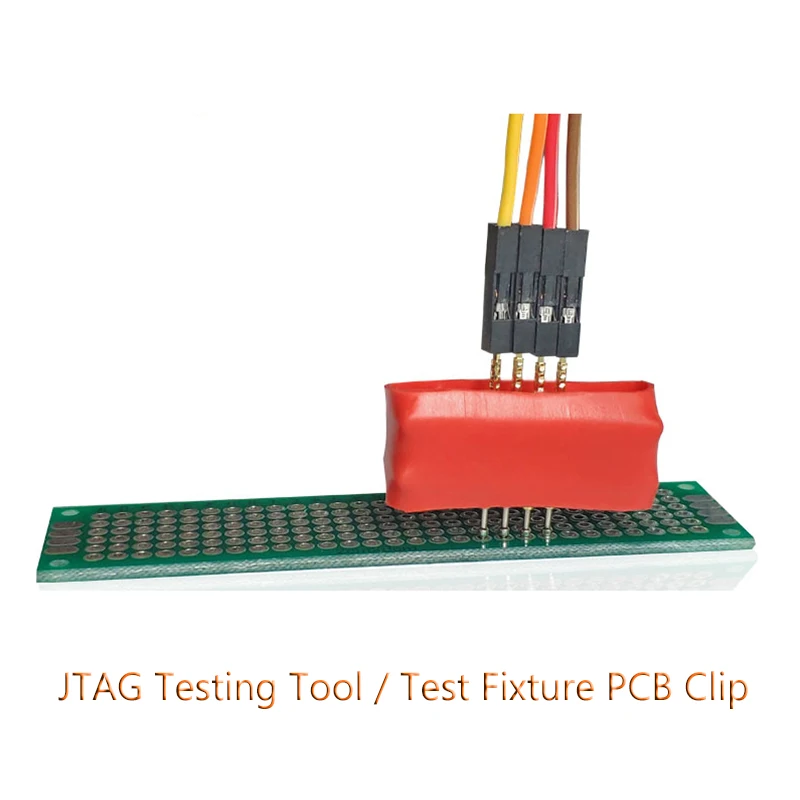

Cosa considerare per la scansione del confine (JTAG)

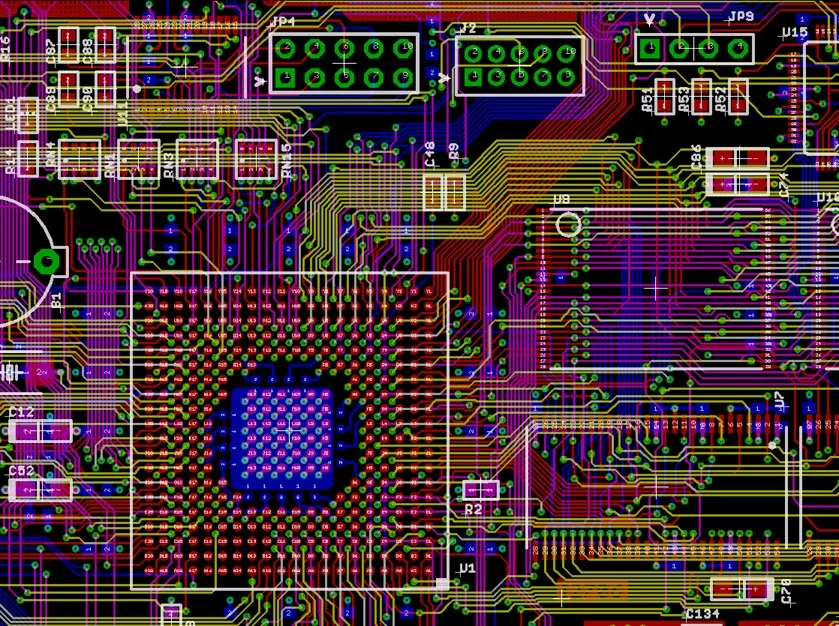

I componenti composti da griglie complesse basate su elementi complessi forniscono agli ingegneri addetti ai test solo un numero limitato di punti di prova accessibili. Anche in questi casi, la testabilità può comunque essere migliorata. Le tecnologie boundary scan e integrated self-test (IST) possono essere impiegate per ridurre i tempi di completamento dei test e migliorarne l'efficacia.

Sia per gli ingegneri di sviluppo che per quelli di test, definire una strategia di test basata sulle tecnologie boundary scan e IST comporta inevitabilmente un aumento dei costi. Gli ingegneri di sviluppo devono integrare componenti boundary scan (standard IEEE-1149.1) nel circuito e garantire l'accessibilità di specifici pin di test (ad esempio, ingresso dati di test - TDI, uscita dati di test - TDO, clock di test - TCK, selezione modalità di test - TMS ed eventualmente reset di test).

Gli ingegneri addetti ai test creano un modello BSDL (Boundary Scan Description Language) per il dispositivo. In questa fase, devono sapere quali funzioni e comandi di boundary scan sono supportati dal dispositivo. Il test boundary scan può diagnosticare cortocircuiti e interruzioni fino al livello del filo. Inoltre, se specificato dall'ingegnere di sviluppo, il built-in self-test (BIST) del componente può essere attivato tramite il comando boundary scan "RunBIST". Soprattutto nei circuiti contenenti numerosi ASIC e altri componenti complessi in cui i modelli di test convenzionali non sono disponibili, i componenti boundary scan possono ridurre significativamente i costi di sviluppo dei modelli di test.

L'entità della riduzione di tempi e costi varia a seconda del componente. Per un circuito contenente un circuito integrato che richiede una copertura dei guasti di 100%, sono in genere necessari circa 400.000 vettori di test. Utilizzando il boundary scan, il numero di vettori di test può essere ridotto a poche centinaia mantenendo la stessa percentuale di copertura dei guasti. Pertanto, l'approccio boundary scan offre vantaggi distinti quando i modelli di test non sono disponibili o l'accesso ai nodi del circuito è limitato. La decisione di adottare il boundary scan dipende dal bilanciamento dei costi crescenti durante lo sviluppo, l'utilizzo e la produzione. Il boundary scan deve essere valutato in base al tempo di rilevamento dei guasti richiesto, al tempo di test, al time-to-market e ai costi degli adattatori, puntando al massimo risparmio sui costi. In molti casi, un approccio ibrido che combina i tradizionali metodi di test in-circuit con il boundary scan si rivela la soluzione ottimale.

Benchuang Electronics offre prodotti di alta qualità Layout del PCB e PCB ad alta velocità servizi. Contattateci e inviateci le vostre specifiche.