Durante el diseño de PCB, ¿cómo podemos garantizar el funcionamiento eficiente de la memoria flash y otros componentes programables?

La programación de la memoria flash a veces puede tardar mucho tiempo (hasta un minuto para memorias o bancos de memoria grandes). Por lo tanto, se debe evitar la inversión de la unidad desde otros componentes durante este período, ya que podría dañar la memoria flash. Para evitarlo, todos los componentes conectados a las líneas de control del bus de direcciones deben estar en estado de alta impedancia. Asimismo, el bus de datos también debe poder aislarse para garantizar que la memoria flash esté descargada y lista para la programación posterior.

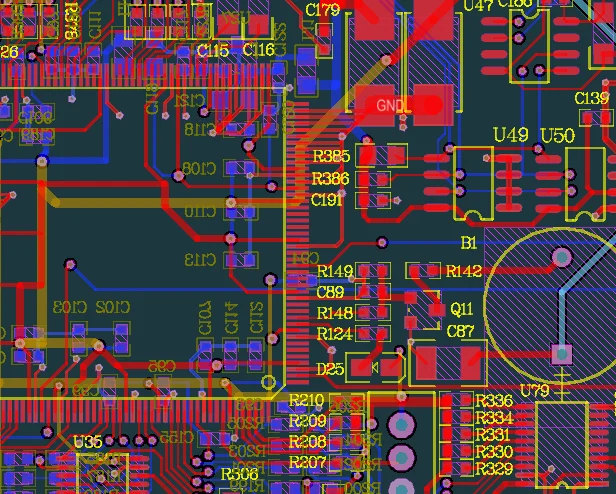

Los componentes programables en el sistema (ISP), como los de Altera, Xilinx y Lattice, tienen requisitos específicos, así como otras consideraciones especiales. Además de garantizar los requisitos de testabilidad mecánica y eléctrica, es necesario garantizar la capacidad de programación y verificación de datos. Para los componentes de Altera y Xilinx, se utiliza el formato vectorial en serie (SVF), que recientemente se ha convertido en un estándar casi industrial. Muchos sistemas de prueba pueden programar estos dispositivos y utilizar los datos de entrada del SVF para generar señales de prueba.

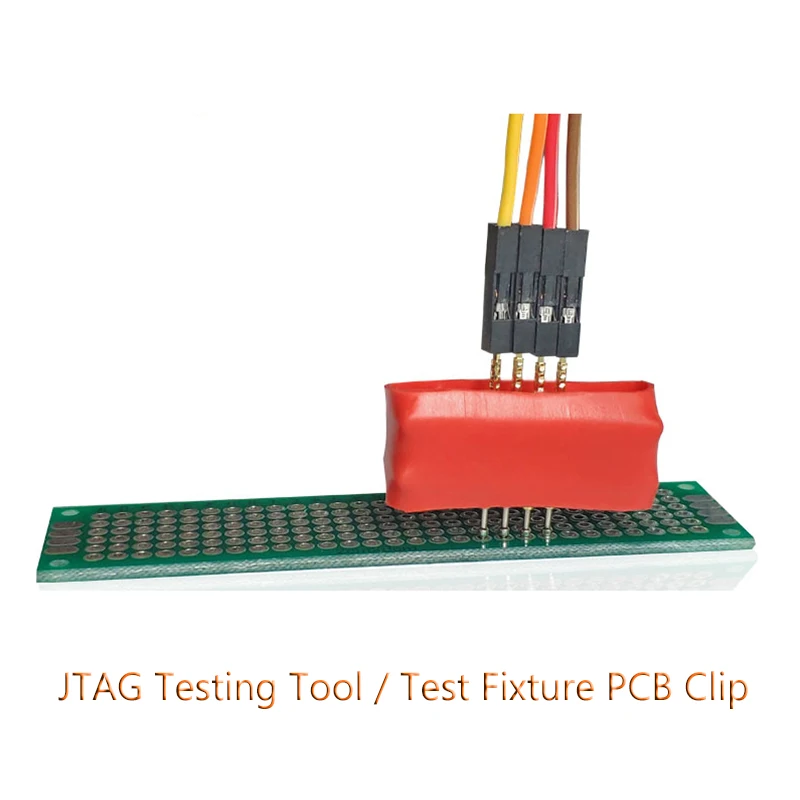

La programación de estos dispositivos mediante la Cadena de Escaneo de Límites (JTAG) también utiliza el formato de datos seriales. Al compilar los datos de programación, es crucial considerar toda la cadena de dispositivos dentro del circuito; los datos no deben limitarse únicamente al dispositivo que se está programando. Durante la programación, el generador automático de señales de prueba considera toda la cadena de componentes e incorpora otros componentes en un modelo de derivación.

Por el contrario, Lattice requiere datos en formato JEDEC y realiza programación paralela mediante puertos de entrada y salida estándar. Tras la programación, los datos también se utilizan para verificar la funcionalidad del componente. Los datos proporcionados por el departamento de desarrollo deben ser lo más fácilmente utilizables posible por el sistema de pruebas directamente o con una conversión mínima.

Qué tener en cuenta para el escaneo de límites (JTAG)

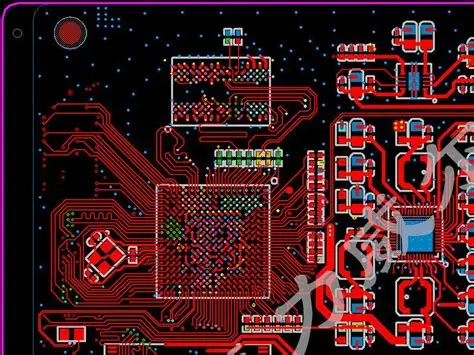

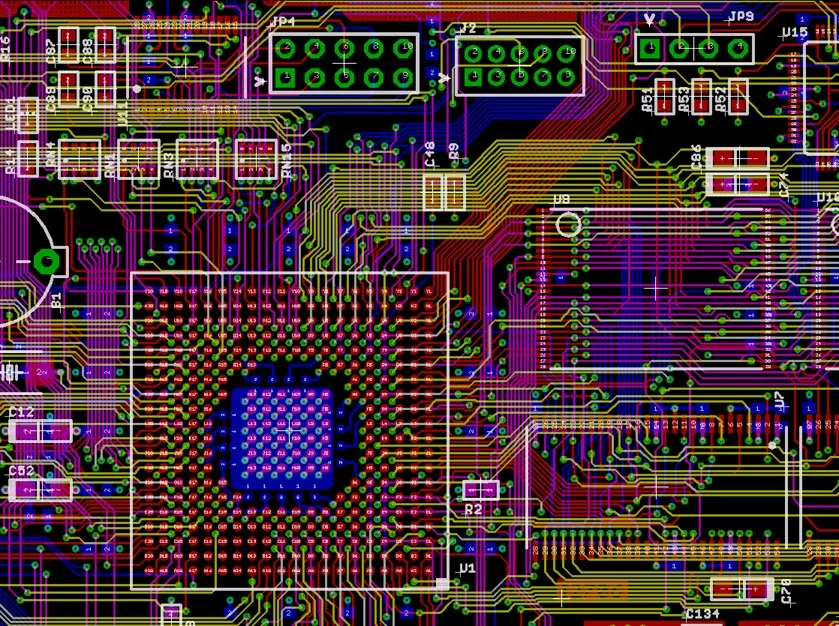

Los componentes compuestos por cuadrículas intrincadas basadas en elementos complejos proporcionan a los ingenieros de pruebas un número limitado de puntos de prueba accesibles. Incluso en estos casos, se puede mejorar la testabilidad. Se pueden emplear tecnologías de escaneo de límites y autoprueba integrada (IST) para reducir el tiempo de finalización de las pruebas y mejorar su eficacia.

Tanto para los ingenieros de desarrollo como para los de pruebas, establecer una estrategia de pruebas basada en tecnologías de escaneo de límites e IST inevitablemente incrementa los costos. Los ingenieros de desarrollo deben incorporar componentes de escaneo de límites (estándar IEEE-1149.1) en el circuito y garantizar el acceso a los pines de prueba específicos (p. ej., entrada de datos de prueba - TDI), salida de datos de prueba - TDO, reloj de prueba - TCK, selección de modo de prueba - TMS y, posiblemente, reinicio de prueba).

Los ingenieros de pruebas crean un modelo de lenguaje de descripción de escaneo de límites (BSDL) para el dispositivo. En esta etapa, deben conocer las funciones y comandos de escaneo de límites que admite el dispositivo. Las pruebas de escaneo de límites pueden diagnosticar cortocircuitos y aperturas, incluso a nivel de cable. Además, si el ingeniero de desarrollo lo especifica, la autoprueba integrada (BIST) del componente puede activarse mediante el comando de escaneo de límites "RunBIST". Especialmente en circuitos que contienen numerosos ASIC y otros componentes complejos donde no se dispone de modelos de prueba convencionales, los componentes de escaneo de límites pueden reducir significativamente el coste de desarrollo de modelos de prueba.

El grado de reducción de tiempo y costos varía según el componente. Para un circuito con un CI que requiere cobertura de fallas 100%, se requieren aproximadamente 400,000 vectores de prueba. Al emplear el escaneo de límites, el número de vectores de prueba se puede reducir a unos pocos cientos, manteniendo la misma tasa de cobertura de fallas. Por lo tanto, el enfoque de escaneo de límites ofrece claras ventajas cuando no se dispone de modelos de prueba o el acceso a los nodos del circuito es restringido. La decisión de adoptar el escaneo de límites depende de equilibrar el aumento de costos durante el desarrollo, la utilización y la fabricación. El escaneo de límites debe sopesarse con el tiempo requerido de detección de fallas, el tiempo de prueba, el tiempo de comercialización y los costos del adaptador, buscando maximizar el ahorro. En muchos casos, un enfoque híbrido que combina métodos tradicionales de prueba en circuito con el escaneo de límites resulta ser la solución óptima.

Benchuang Electronics ofrece alta calidad Diseño de PCB y PCB de alta velocidad Servicios. Contáctenos y envíenos sus especificaciones.