Wie können wir während des PCB-Layouts einen effizienten Betrieb des Flash-Speichers und anderer programmierbarer Komponenten gewährleisten?

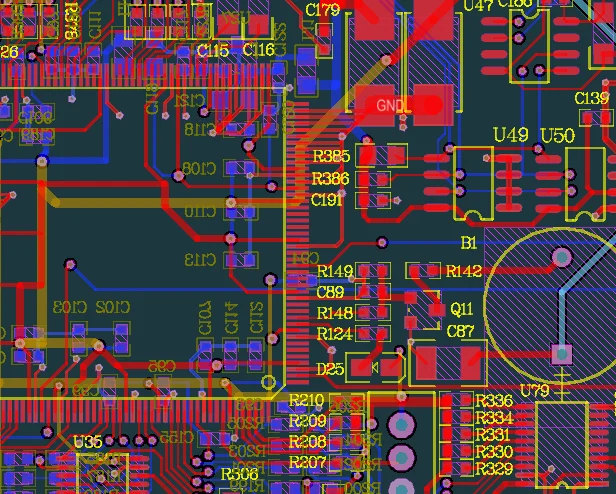

Die Programmierung von Flash-Speichern kann mitunter längere Zeit in Anspruch nehmen (bis zu einer Minute bei großen Speichern oder Speicherbänken). Daher muss während dieser Zeit ein Rücksteuern durch andere Komponenten verhindert werden, da dies den Flash-Speicher beschädigen könnte. Um dies zu vermeiden, müssen alle an die Steuerleitungen des Adressbusses angeschlossenen Komponenten hochohmig betrieben werden. Ebenso muss der Datenbus trennbar sein, um sicherzustellen, dass der Flash-Speicher entladen und für die nachfolgende Programmierung bereit ist.

In-System-programmierbare (ISP) Komponenten, wie beispielsweise von Altera, Xilinx und Lattice, stellen spezifische Anforderungen und erfordern weitere besondere Aspekte. Neben der Sicherstellung der mechanischen und elektrischen Testbarkeit muss die Programmierbarkeit und die Verifizierung von Daten gewährleistet sein. Für Altera- und Xilinx-Komponenten kommt das Serial Vector Format (SVF) zum Einsatz, das sich in letzter Zeit zu einem nahezu branchenweiten Standard entwickelt hat. Viele Testsysteme können solche Bausteine programmieren und die Eingangsdaten im SVF zur Generierung von Testsignalen nutzen.

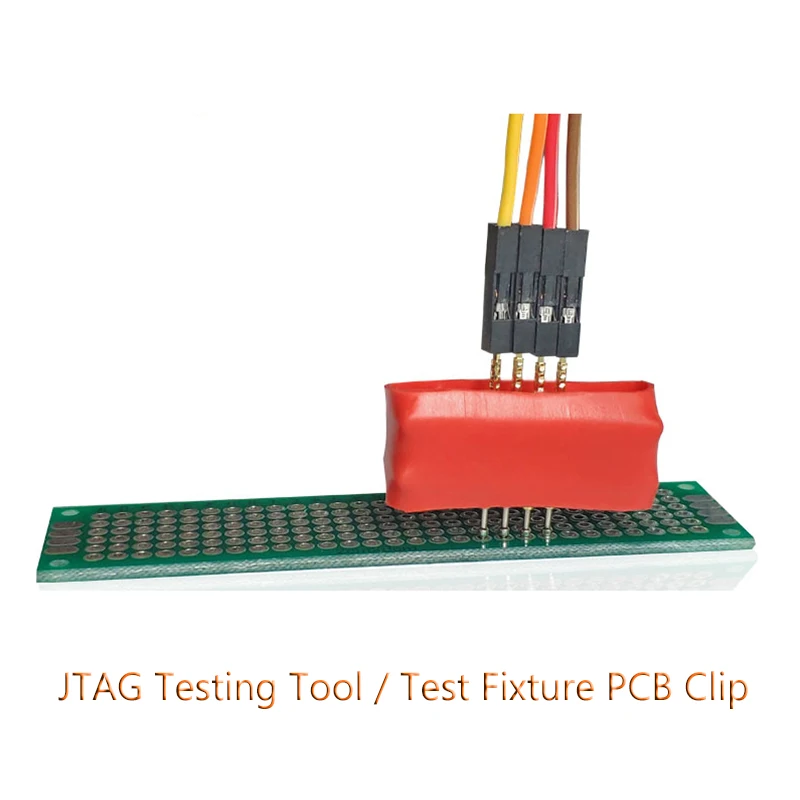

Die Programmierung dieser Geräte über die Boundary-Scan-Chain (JTAG) nutzt ebenfalls das serielle Datenformat. Beim Kompilieren der Programmierdaten ist es entscheidend, die gesamte Gerätekette im Schaltkreis zu berücksichtigen; die Daten dürfen nicht allein auf das zu programmierende Gerät beschränkt werden. Während der Programmierung berücksichtigt der automatische Testsignalgenerator die gesamte Komponentenkette und integriert weitere Komponenten in ein Bypass-Modell.

Lattice hingegen benötigt Daten im JEDEC-Format und führt parallele Programmierung über Standard-Ein- und Ausgänge durch. Nach der Programmierung werden die Daten auch zur Überprüfung der Komponentenfunktionalität verwendet. Die von der Entwicklungsabteilung bereitgestellten Daten sollten vom Testsystem möglichst direkt oder mit minimaler Konvertierung verwendet werden können.

Was bei der Boundary-Scan-Methode (JTAG) zu beachten ist

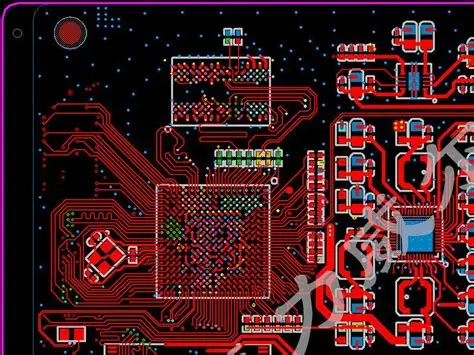

Komponenten mit komplexen Gittern, die auf vielschichtigen Elementen basieren, bieten Testingenieuren nur eine begrenzte Anzahl zugänglicher Testpunkte. Selbst in solchen Fällen lässt sich die Testbarkeit verbessern. Durch den Einsatz von Boundary-Scan- und integrierten Selbsttest-Technologien (IST) können die Testdauer verkürzt und die Testeffektivität erhöht werden.

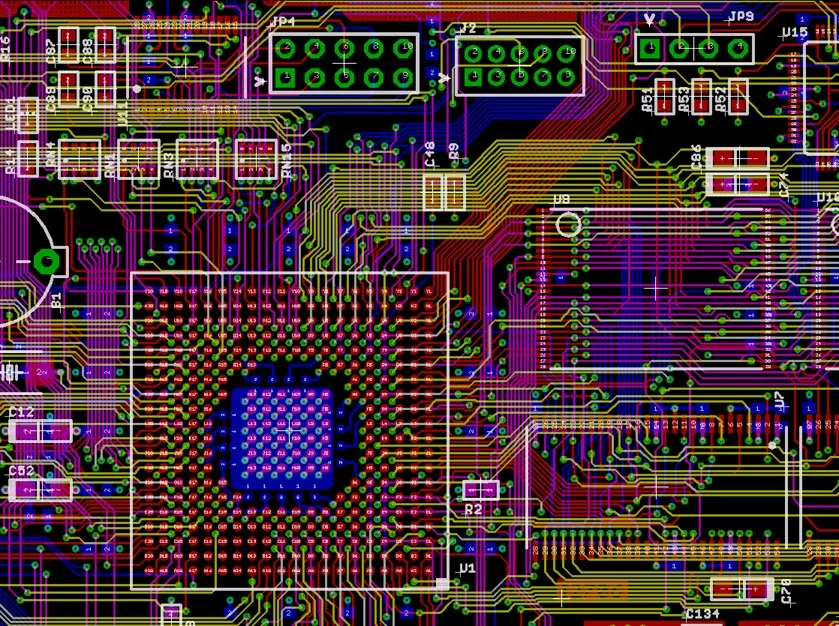

Für Entwicklungs- und Testingenieure führt die Etablierung einer Teststrategie auf Basis von Boundary-Scan- und IST-Technologien zwangsläufig zu höheren Kosten. Entwicklungsingenieure müssen Boundary-Scan-Komponenten (IEEE-1149.1-Standard) in die Schaltung integrieren und sicherstellen, dass bestimmte Test-Pins zugänglich sind (z. B. Testdateneingang – TDI, Testdatenausgang – TDO, Testtakt – TCK, Testmodusauswahl – TMS und gegebenenfalls Testreset).

Testingenieure erstellen ein BSDL-Modell (Boundary Scan Description Language) für das Bauteil. Dazu müssen sie wissen, welche Boundary-Scan-Funktionen und -Befehle das Bauteil unterstützt. Mit Boundary-Scan-Tests lassen sich Kurzschlüsse und Unterbrechungen bis auf Leiterebene diagnostizieren. Zusätzlich kann, falls vom Entwicklungsingenieur spezifiziert, der integrierte Selbsttest (BIST) der Komponente über den Boundary-Scan-Befehl “RunBIST” ausgelöst werden. Insbesondere in Schaltungen mit zahlreichen ASICs und anderen komplexen Bauteilen, für die keine herkömmlichen Testmodelle verfügbar sind, können Boundary-Scan-Komponenten die Kosten für die Entwicklung von Testmodellen erheblich reduzieren.

Das Ausmaß der Zeit- und Kostenreduzierung variiert je nach Komponente. Für eine Schaltung mit einem IC, der eine Fehlerabdeckung von 100% erfordert, werden typischerweise etwa 400.000 Testvektoren benötigt. Durch den Einsatz von Boundary Scan kann die Anzahl der Testvektoren auf wenige Hundert reduziert werden, ohne die Fehlerabdeckungsrate zu beeinträchtigen. Daher bietet der Boundary-Scan-Ansatz deutliche Vorteile, wenn keine Testmodelle verfügbar sind oder der Zugang zu Schaltungsknoten eingeschränkt ist. Die Entscheidung für Boundary Scan hängt von der Abwägung der erhöhten Kosten während Entwicklung, Nutzung und Fertigung ab. Boundary Scan muss gegen die erforderliche Fehlererkennungszeit, Testzeit, Markteinführungszeit und Adapterkosten abgewogen werden, um maximale Kosteneinsparungen zu erzielen. In vielen Fällen erweist sich ein hybrider Ansatz, der traditionelle In-Circuit-Testmethoden mit Boundary Scan kombiniert, als optimale Lösung.

Benchuang Electronics bietet hochwertige PCB-Layout und Hochgeschwindigkeits-Leiterplatte Dienstleistungen. Nehmen Sie Kontakt mit uns auf und senden Sie uns Ihre Spezifikationen.