Leitfaden für Hochgeschwindigkeits-PCB-Design: Entwurf von High-Density (HD)-Schaltungen

Die Kontaktflächen (Pads), die grundlegenden Bausteine der Oberflächenmontage, bilden das Leiterbahnmuster auf einer Leiterplatte. Dieses Muster besteht aus verschiedenen Kontaktflächenkombinationen, die für bestimmte Bauteiltypen ausgelegt sind. Kontaktflächen dienen als teilweise leitende Bereiche für elektrische Verbindungen, zur Befestigung von Bauteilen oder beides.

Die Geometrie der Lötpads kann je nach Lötverfahren für die Montage elektronischer Bauteile variieren. Wo möglich, sollten die Padformen so definiert werden, dass sie den verwendeten Montageprozess nicht beeinflussen. Unabhängig davon, ob die Bauteile ein- oder beidseitig auf der Leiterplatte montiert werden und ob Wellen-, Reflow- oder andere Lötverfahren zum Einsatz kommen, müssen die Abmessungen der Lötpads und Bauteile optimiert werden, um eine einwandfreie Lötverbindung und die Einhaltung der Prüfnormen zu gewährleisten. Obwohl die Padmuster dimensionell definiert sind und zur Geometrie der Leiterplatte gehören, unterliegen sie Fertigungstoleranzen und Einschränkungen im Zusammenhang mit Beschichtung, Ätzung, Montage und anderen Bedingungen. Auch die Verwendung von Lötstopplack und die Ausrichtung zwischen Lötstopplack und Leiterbahnen beeinflussen die Fertigungstauglichkeit.

1. Anforderungen an die Polsterung

Die Norm IEC 61188 der Internationalen Elektrotechnischen Kommission erkennt die Notwendigkeit unterschiedlicher Zielsetzungen hinsichtlich der Lötstellen- bzw. Lötpad-Überstandsbedingungen an. Diese neue internationale Norm bestätigt zwei grundlegende Ansätze zur Entwicklung von Padformen:

1) Präzise Daten basierend auf industriellen Bauteilspezifikationen, Leiterplattenfertigungskapazitäten und Bauteilplatzierungsgenauigkeit. Diese Padformen sind spezifisch für ein bestimmtes Bauteil und werden durch eine Padformnummer identifiziert.

2) Gleichungen, mit denen sich gegebene Informationen modifizieren lassen, um eine robustere Lötverbindung zu erzielen. Dies ist in Sonderfällen anwendbar, in denen die Präzision der Platzierungs- oder Montagevorrichtungen stärker oder schwächer von den bei der Bestimmung der Pad-Details angenommenen Werten abweicht.

Die Norm definiert maximale, mittlere und minimale Materialbedingungen für Kontaktflächen zur Montage verschiedener Stifte oder Bauteilanschlüsse. Sofern nicht anders angegeben, ordnet diese Norm alle drei Zielwerte den Stufen 1, 2 oder 3 zu.

Stufe 1: Maximal – Bei Anwendungen mit geringer Packungsdichte wird die “maximale” Pad-Konfiguration für das Wellen- oder Reflow-Löten von gehäuselosen Chipbauteilen und Bauteilen mit Kühlrippen und Anschlüssen verwendet. Die für diese Bauteile sowie für Bauteile mit nach innen gerichteten J-förmigen Anschlüssen konfigurierte Geometrie bietet ein größeres Prozessfenster für das manuelle Löten und das Reflow-Löten.

Stufe 2: Mittel – Für Produkte mit moderater Bauteildichte eignet sich diese “mittlere” Lötpad-Geometrie. Sie ähnelt der Standard-Lötpad-Geometrie nach IPC-S-782 und bietet für alle Bauteiltypen robuste Lötbedingungen für Reflow-Prozesse. Zudem sind die Bedingungen für das Wellen- oder Fließlöten von bleifreien und flügelbestückten Bauteilen ausreichend.

Stufe 3: Minimal – Produkte mit hoher Bauteildichte (typischerweise tragbare Anwendungen) können die “minimale” Pad-Geometrie in Betracht ziehen. Die Auswahl einer minimalen Pad-Geometrie ist jedoch möglicherweise nicht für alle Produkte geeignet. Vor der Anwendung minimaler Pad-Formen sollten Produktbeschränkungen berücksichtigt und Tests gemäß den in der Tabelle aufgeführten Bedingungen durchgeführt werden.

Die in IPC-SM-782 bereitgestellten und in IEC 61188 definierten Pad-Geometrien sollten Bauteiltoleranzen und Prozessschwankungen berücksichtigen. Obwohl die Pads im IPC-Standard für die meisten Montageanwendungen eine robuste Schnittstelle bieten, haben einige Unternehmen den Bedarf an minimalen Pad-Geometrien für tragbare Elektronik und andere spezielle Anwendungen mit hoher Packungsdichte geäußert.

Der internationale Pad-Standard (IEC 61188) berücksichtigt die Anforderungen von Anwendungen mit höherer Bauteildichte und liefert Informationen zu Pad-Geometrien für spezifische Produkttypen. Diese Informationen spezifizieren geeignete Abmessungen, Formen und Toleranzen für SMD-Pads, um eine ausreichende Fläche für eine ordnungsgemäße Lötkehlnahtbildung zu gewährleisten und gleichzeitig die Inspektion, Prüfung und Nachbearbeitung dieser Lötstellen zu ermöglichen.

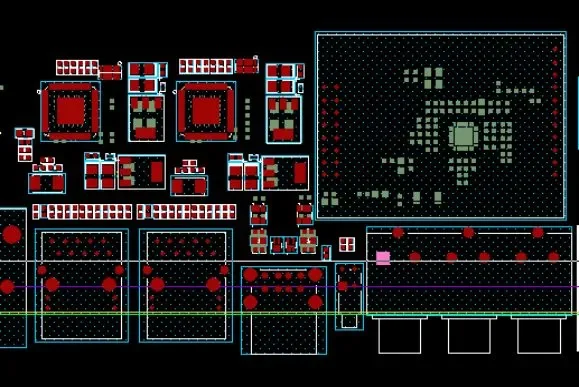

2. BGA und CAP

Die BGA-Gehäusetechnik wurde weiterentwickelt, um den aktuellen Lötmontagetechniken gerecht zu werden. Kunststoff- und Keramik-BGA-Bauteile weisen relativ große Kontaktabstände (1,50, 1,27 und 1,00 mm) auf, während Chip-Scale-BGAs Rasterabstände von 0,50, 0,60 und 0,80 mm besitzen. Sowohl Standard-BGAs als auch Fine-Pitch-BGAs sind im Vergleich zu ICs in Fine-Pitch-Pinframe-Gehäusen weniger anfällig für Beschädigungen. Der BGA-Standard erlaubt die selektive Reduzierung der Kontaktpunkte, um spezifische Ein-/Ausgabe-Anforderungen (I/O) zu erfüllen. Bei der Festlegung des Kontaktpunkt-Layouts und der Anschlussbelegung für BGA-Bauteile müssen Gehäuseentwickler neben den Abmessungen und der Form des Chipblocks auch das Chipdesign berücksichtigen. Ein weiteres Problem bei der technischen Anschlussbelegung ist die Chipausrichtung (ob die Pads des Chipmoduls nach oben oder unten zeigen). Die “Face-Up”-Konfiguration für Chipmodule wird typischerweise verwendet, wenn Hersteller die COB-Technologie (Chip-on-Board) einsetzen.

Die Konstruktion der Komponenten und die verwendeten Materialien sind in diesem Industriestandard und dieser Richtlinie nicht definiert. Jeder Hersteller ist bestrebt, seine spezifische Struktur an die vom Anwender definierten Anwendungsanforderungen anzupassen. So können beispielsweise Konsumprodukte in relativ unproblematischen Umgebungen eingesetzt werden, während industrielle Anwendungen oder Anwendungen im Automobilbereich häufig unter deutlich höheren Belastungen funktionieren müssen. Abhängig von den physikalischen Eigenschaften der für die BGA-Fertigung ausgewählten Materialien können Flip-Chip- oder Drahtbondverfahren zum Einsatz kommen. Da die Chip-Montagestruktur starr ist, ist die Montagebasis des Chipmoduls typischerweise mit Leitern zentriert, wobei die Signale von den Chipmodul-Pads zu einer Anordnung von Kontaktkugeln geführt werden.

Das in diesem Dokument beschriebene Grid-Array-Gehäuse ist in der JEDEC-Publikation 95 enthalten. Quadratische BGAs: JEDEC MS-028 definiert eine kleinere, rechteckige Kunststoff-BGA-Komponentenkategorie mit einem Kontaktabstand von 1,27 mm. Die Abmessungen dieser Matrixkomponente ermöglichen eine hohe Flexibilität hinsichtlich Pin-Abstand, Kontaktmatrix-Layout und Konstruktion. JEDEC MO-151 definiert verschiedene kunststoffgekapselte BGAs. Quadratische Profile decken Abmessungen von 7,0 bis 50,0 mm ab, mit drei Kontaktabstandsoptionen: 1,50 mm, 1,27 mm und 1,00 mm.

Die Kugelkontakte können in einem einheitlichen Muster angeordnet sein, wobei die Reihen und Spalten in gerader oder ungerader Anzahl angeordnet sind. Die Anordnung muss zwar über die gesamte Gehäuseform symmetrisch sein, Komponentenhersteller dürfen jedoch die Anzahl der Kontaktstellen innerhalb bestimmter Bereiche reduzieren.

Benchuang Electronics bietet hochwertige PCB-Layout und Hochgeschwindigkeits-Leiterplatte Dienstleistungen. Nehmen Sie Kontakt mit uns auf und senden Sie uns Ihre Spezifikationen.