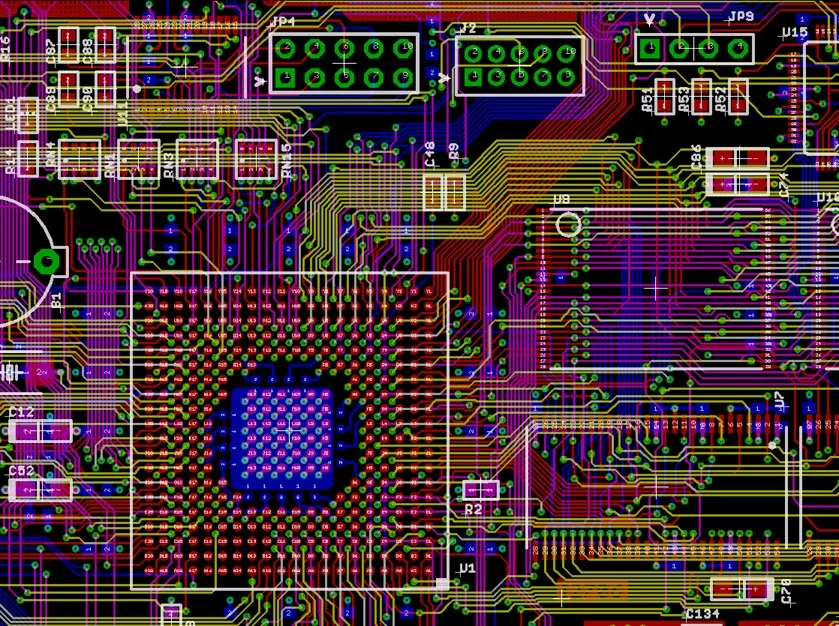

BenChuang Electronics fertigt HDI- und Ultrafeinleiter-Leiterplatten für Telekommunikation, Automobilindustrie, Medizintechnik, industrielle Steuerungstechnik und Halbleitertechnik. Wir unterstützen Prototypen-, Pilot- und Serienfertigung mit stabilen Prozessen wie Laserbohren, LDI-Belichtung, sequenzieller Laminierung, Via-in-Pad, Kupferfüllung und Impedanzkontrolle.

1) Feine Linie / Raum: Was wir festhalten

Stabile Produktionsregeln (konservativ, massentauglich):

- Mindestzeilen/Abstände: 3/3 mil (≈75/75 µm) über qualifizierte Materialien

- Typisches Kupfer: 1/2–1 oz äußere Schichten; 1/3–1/2 oz innere Schichten für feine Linien

- Anmeldung: Die Ausrichtung der Vorlage auf die Lötstoppmaske wird mit LDI und optischen Passmarken präzise gesteuert.

- BGA-Flucht: zuverlässiges Routing bei 0,35 mm Steigung mit geeigneter Pad-/Via-Strategie

Wie wir Stabilität gewährleisten

- LDI für gleichmäßige Belichtung; feinkörniger Resist zur Reduzierung von Hinterschneidungen

- Ätzkompensation pro Panelzone; Kupferausgleich auf gegenüberliegenden Schichten

- SPC auf kritischen Abmessungen (Linienbreite, Ringbreite) mit periodischen Mikroschnitten

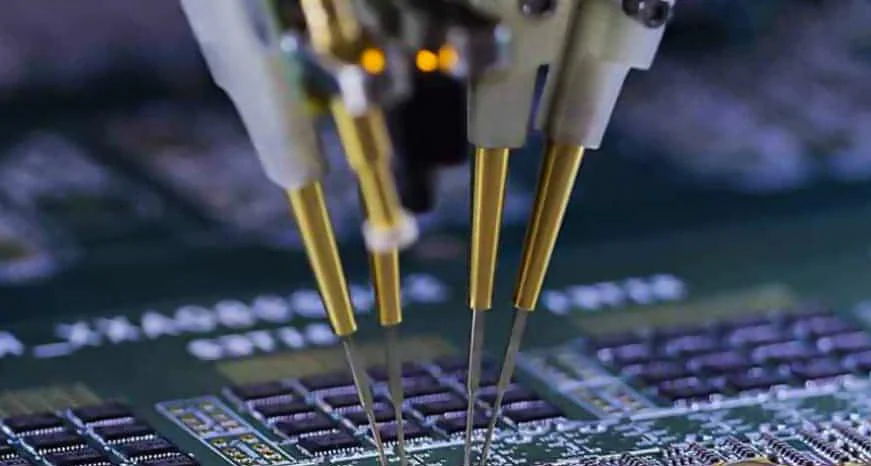

2) Mikrovia-Strukturen: Größe, Füllung, Stapelstrategie

Fähigkeiten

- Laser-Mikrovia-Durchmesser: 4–8 mil (≈0,10–0,20 mm), dielektrische Dicke angepasst, um ein Aspektverhältnis von ≤ 0,8 zu gewährleisten

- Blind/vergraben/gestapelt: versetzte oder gestapelte uVias; Stapelhöhe wird von Fall zu Fall geprüft

- Via-in-pad (VIP): mit Harz gefüllt und ummantelt oder kupfergefüllt für flache Auflageflächen und zuverlässige Montage

- Rückbohrung: Verfügbar zur Entfernung von Stubs in Hochgeschwindigkeitsnetzen

Prozesssteuerungen

- Laserenergiekalibrierung mittels dielektrischer Messanordnung; Querschnitte der Proben aus jeder Charge

- Fülldichte- und Hohlraumprüfung; Ebenheitskontrolle nach dem Befüllen und Abdecken

- Thermische Spannungsqualifizierung für gestapelte Strukturen auf neuen Stapelaufbauten

3) Kontrollierte Impedanz: Design-to-Measure-Schleife

Designunterstützung

- Vorbereitende Hinweise zum Layout Zielimpedanz (z.B, 50 Ω/90 Ω/100 Ω (einseitig/differenziell)

- Material- und Folienauswahl (bei Bedarf verlustarm), Wahl des Glastyps und Zielvorgaben für den Harzgehalt

- Verifizierte Feldsolver-Stackups (Kern vs. Prepreg, RCC, wo zutreffend)

Fertigung und Validierung

- Impedanz-Coupon auf jedem Panel; TDR-Messung pro Charge protokolliert

- Typische Toleranz: ±10% (Auf Wunsch engere Passgenauigkeit bei abgestimmten Material-/Folien-/Prozessfenstern)

- Die Kupferrauheit und der Ätzfaktor wurden in Abhängigkeit von der Enddicke modelliert, um den Zielwert Z zu erreichen.

4) Materialien & Stapelaufbauten (Beispiele, die wir häufig verwenden)

- FR-4-Systeme: Hochtransparenter FR-4 für gängige HDI-Systeme; RCC-Optionen für feinere Leitungen

- Optionen mit geringem Verlust: Für HF-/Hochgeschwindigkeitsschichten können Hybridaufbauten ausgewertet werden

- Oberflächenbehandlungen: ENIG / ENEPIG / Imm-Silber / OSP; Oberflächenbeschaffenheit nach Rastermaß, Drahtbondierungs- oder Korrosionsanforderungen

- Thermische Auslegung: Kupferausgleich, Leiterbahnverläufe und Via-in-Pads mit Füllung zur Minderung von Verformungen auf großen Leiterplatten

Wir stellen vor der CAM-Freigabe eine Fertigungsaufbauzeichnung zur Verfügung, die Foliendicke, Dielektrikumdicke, Glasarten und Zielimpedanztabellen enthält.

5) Qualitäts- und Zuverlässigkeitskontrollen

- Inspektion: 100% AOI auf inneren/äußeren Lagen; Röntgenprüfung von BGA/VIP; Flying-Probe-/ICT-basierte Fertigungsstufe

- Zuverlässigkeit: Thermische Zyklenprüfung/Thermoschockprüfung neuer Stackups; Lötbarkeitsprüfungen pro Charge

- Rückverfolgbarkeit: Prozessdatensätze auf Chargenebene, die mit Coupondaten und Materialien verknüpft sind

- KPIs (intern überwacht): Erstausbeute, termingerechte Lieferung und RMA-Quote im Außendienst; Korrekturmaßnahmen bis zum Abschluss nachverfolgt.

6) Praktische DFM-Regeln (Ingenieurfreundlich)

- Zeilen/Leerzeichen: kritische Netze müssen bei ≥ 3/3 Mio. Sofern nicht vorher genehmigt; Lockerung der Vorschriften für nicht kritische Netze zur Ertragssteigerung

- Ringförmiger Ring: Design für ≥ 3 Mio. bei Laser-Vias; Pad-Stack besprechen, falls engere Belegung gewünscht ist

- Dielektrikum: Die dielektrische Schichtdicke der Mikrovia pro Lagenpaar muss so eingestellt werden, dass das Aspektverhältnis ≤ 0,8 beträgt.

- Impedanz: Vermeiden Sie die Mischung verschiedener Glasarten über die Spiegelschichten hinweg; überprüfen Sie die Kupferverteilung, um Verzerrungen zu reduzieren.

- VIP: Bitte halten Sie VIP-Bereiche fern; wir informieren Sie über die Mindestmaße für Maskenfreiheit und Kappenstärke.

Wir teilen ein kurzes, einseitiges Dokument. HDI DFM Checkliste während der Angebotsanfrage, damit die Layout-Teams die Regeln frühzeitig festlegen und Änderungsmitteilungen in der Schlussphase vermeiden können.

7) Fallbeispiel (Typischer HDI-Aufbau)

- Anwendung: 5G-Funkmodul, Mixed-Signal und Hochgeschwindigkeit

- Stapel: 10-lagiger HDI mit Mikrovias L1–L2/L9–L10, versetzt zu L3/L8

- Ziele: 100 Ω differentiell (Hochgeschwindigkeitspaare), 50 Ω unsymmetrisch (HF)

- Taktik: Verlustarme Kerne für Hochgeschwindigkeitsschichten, Kupferausgleich auf Stromversorgungsebenen, VIP unter BGA mit feiner Rasterteilung

- Ergebnis: Gutscheine gemessen innerhalb ±8–9% Zielgenauigkeit erreicht; Koplanarität der Montage auf VIP-Pads sichergestellt; nach Reflow-Profilierung keine Verformungsprobleme.

8) Was Sie in Ihre Angebotsanfrage aufnehmen sollten (Beschleunigt die Angebotserstellung)

- Gerber/ODB++, Netzliste (falls verfügbar), vorläufige Impedanzberechnung oder Zielimpedanz

- Lagenanzahl, Platinendicke, Mindestzeile/Abstand, min via (Laser/mechanisch)

- VIP-/Kupferfüllungsanforderungen, Oberflächenbeschaffenheit, Kupfergewichte pro Schicht

- Lötstopplackfarbe/Glanz, Legende, Panelisierungspräferenz

- Teststrategie (Flying-Probe/ICT), spezielle Reinheits- oder Ionenanforderungen

- Erwartungen an die Vorlaufzeit von Prototypen im Vergleich zur Serienproduktion

Warum BenChuang

Stabile Ausbeuten bei feinen Leiterbahnen, präzise Mikrovia-Prozesse und eine geschlossene Impedanzregelung vom Design bis zur Coupon-Messung – das macht HDI-Aufbauten bei uns reproduzierbar. Für Ihr nächstes NPI- oder Serienprojekt senden Sie uns Ihre Stackup-Idee und die Zielimpedanz; wir erstellen Ihnen einen fertigungsgerechten Vorschlag mit DFM-Hinweisen und Coupon-Plan.