To address the impacts introduced by the aforementioned transmission line issues, we discuss methods for controlling these effects from the following perspectives.

1. Strictly Control the Routing Length of Critical Netlines

If the design involves high-speed edge transitions, transmission line effects on the PCB must be considered. This issue is particularly prevalent in modern high-frequency clocked integrated circuits. Basic principles for addressing this issue include: - For CMOS or TTL circuits operating below 10MHz, routing length should not exceed 7 inches. - For frequencies up to 50MHz, the routing length should not exceed 1.5 inches. - For frequencies at or above 75MHz, the routing length should be limited to 1 inch. - For GaAs chips, the maximum routing length should be 0.3 inches. Exceeding these standards introduces transmission line effects.

2. Rational Planning of Trace Topology

Another approach to mitigating transmission line effects involves selecting appropriate routing paths and termination topologies. Trace topology refers to the sequence and structural arrangement of a network cable's wiring. When employing high-speed logic devices, signals with rapidly changing edges will be distorted by branch traces on the main signal trunk unless branch lengths are kept extremely short. Typically, PCB routing employs two fundamental topologies: daisy chain routing and star distribution.

In Daisy Chain routing, traces originate from the driver and sequentially reach each receiver. If series resistors are used to modify signal characteristics, they should be positioned immediately adjacent to the driver. Daisy chain routing offers the best performance in controlling high-order harmonic interference on traces. However, this routing method has the lowest routing success rate and rarely achieves 100% routing. In practical design, we minimize stub lengths in daisy chain routing. A safe length value is: Stub Delay <= Trt * 0.1.

For example, stub lengths in high-speed TTL circuits should be less than 1.5 inches. This topology occupies minimal routing space and can be terminated with a single resistor. However, this routing structure causes asynchronous signal reception at different signal receivers.

Star topology effectively avoids clock signal asynchrony issues, but manual routing is complicated on high-density PCBs. Using an automatic router is the best method for achieving star routing. Termination resistors are required on each branch. The resistance value of the termination resistor should match the characteristic impedance of the connection. This can be calculated manually or using CAD tools to determine the characteristic impedance and matching resistor value.

While simple resistors were used in the above examples, more complex termination methods are practical options. The first alternative is RC termination. RC termination reduces power consumption but is only suitable for stable signal conditions. This approach is most effective for clock line matching. A drawback is that the capacitance in RC termination can affect signal shape and propagation speed.

Series resistor termination imposes no additional power loss but slows signal propagation. This method is used in bus driver circuits where timing delays are negligible. Another advantage of series resistor termination is its ability to reduce the number of board components and wiring density.

The final approach is discrete termination, where matching components are placed near the receiver. Its advantages include avoiding signal pull-down and effectively mitigating noise. It is typically used for TTL input signals (ACT, HCT, FAST).

Additionally, the type of packaging and the orientation of the termination resistor must be considered. Generally, SMD surface-mount resistors exhibit lower inductance than through-hole components, making SMD packages the preferred choice. If standard through-hole resistors are selected, two mounting orientations are available: vertical and horizontal.

Vertical mounting keeps one mounting lead short, reducing thermal resistance between the resistor and the board, allowing heat to dissipate more readily into the air. However, taller vertical mounting increases the resistors' inductance. Horizontal mounting offers lower inductance due to its lower profile. Yet, overheated resistors may drift, and in worst-case scenarios, become open circuits, causing the PCB trace termination matching to fail and becoming a potential failure factor.

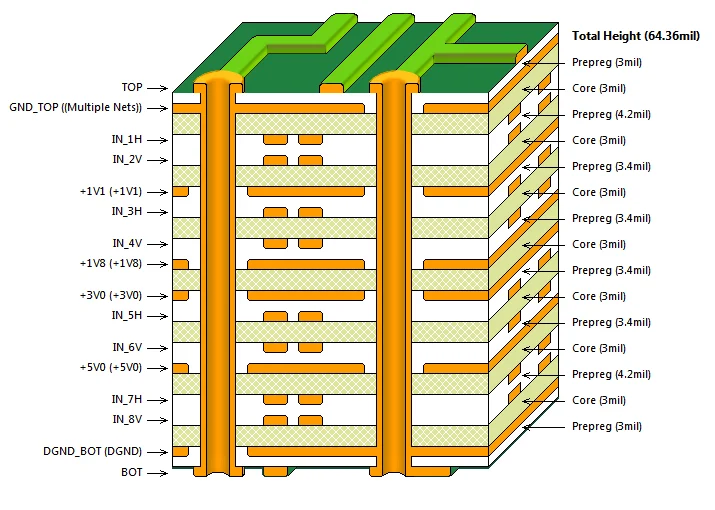

3. Methods for Suppressing Electromagnetic Interference

Effectively addressing signal integrity issues will improve the electromagnetic compatibility (EMC) of PCB boards. Ensuring proper grounding of the PCB is particularly crucial. For complex designs, employing one signal layer paired with one ground layer proves highly effective. Additionally, minimizing signal density on the board's outermost layer is an effective method to reduce electromagnetic radiation. This can be achieved using “surface area stacking” technology or “build-up” design for PCB fabrication. Surface area stacking is implemented by adding thin insulating layers and microvias to penetrate these layers on a standard process PCB. Resistors and capacitors can be buried beneath the surface layer, nearly doubling the trace density per unit area and consequently reducing PCB volume. The reduction in PCB area significantly impacts trace topology, resulting in smaller current loops and shorter branch lengths. Since electromagnetic radiation is approximately proportional to the area of current loops, this reduction is beneficial. Simultaneously, the compact form factor allows the use of high-density pin-count packages. This, in turn, decreases interconnect lengths, further shrinking current loops and enhancing electromagnetic compatibility.

4. Other Applicable Techniques

To mitigate voltage transients on integrated circuit (IC) power supplies, decoupling capacitors should be added to the IC. This effectively suppresses power supply glitches and reduces radiation from power loops on the printed circuit board.

Decoupling capacitors provide optimal glitch smoothing when connected directly to the IC's power pins rather than to the power plane. This explains why some device sockets incorporate decoupling capacitors, while others require these capacitors to be positioned extremely close to the device.

All high-speed and high-power components should be placed as close together as possible to minimize power supply voltage transients.

Without a power plane, long power traces form loops between signal and ground, becoming both radiation sources and susceptible circuits.

A trace forming a loop without crossing the same net or other traces is called an open loop. If the loop crosses other traces on the same net, it forms a closed loop. Both scenarios create antenna effects (wire antennas and loop antennas). Antennas radiate EMI externally while also acting as sensitive circuits themselves. Closed loops are a critical consideration, as their radiation is approximately proportional to the loop area.

Conclusion

High-speed circuit design is an extremely complex process. The methodology described herein specifically addresses these high-speed circuit design challenges. Furthermore, multiple factors requiring consideration during high-speed circuit design often present conflicting priorities. For instance, positioning high-speed components close together may reduce delay but can induce crosstalk and significant thermal effects. Therefore, design decisions necessitate balancing these factors through comprehensive trade-offs—meeting design requirements while minimizing complexity.

Benchuang Electronics offers high-quality PCB layout and High-Speed PCB services. Contact us and send your specifications.