Progettato per il montaggio diretto di chip IC e l'interconnessione di segnali ad alta velocità. Supporta da 1 a 20 strati con microvia e tracce/spazi sottili fino a 0,05 mm, profili ultrasottili e un'eccezionale dissipazione del calore. Dal prototipo alla produzione di massa in soli 7-15 giorni.

Vantaggi principali

Densità ultra elevata e passo fine

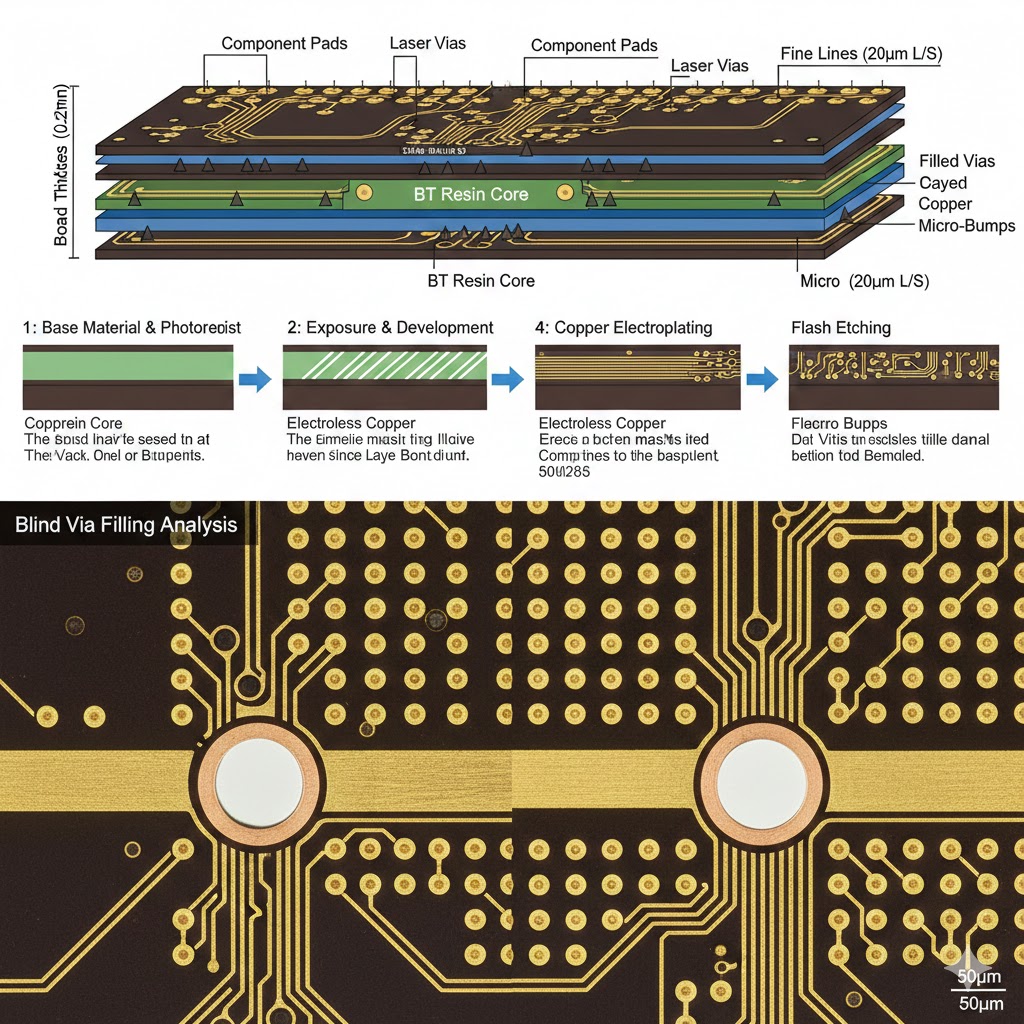

Microvia e tracce/spazi sottili fino a 0,05 mm consentono un routing complesso per il packaging avanzato di circuiti integrati. Un ponte perfetto tra chip e PCB principale per la massima integrazione.

Integrità del segnale superiore e prestazioni ad alta velocità

Ottimizzato per applicazioni RF e ad alta frequenza con materiali a bassa perdita: ideale per moduli 5G, processori AI e calcolo ad alte prestazioni.

Ottima gestione termica

Materiali e design avanzati dissipano in modo efficiente il calore dai chip ad alto consumo energetico, garantendo l'affidabilità dei sistemi ADAS per autoveicoli, dei sistemi di batterie per veicoli elettrici e delle apparecchiature industriali.

Miniaturizzazione e affidabilità

Substrati ultrasottili e leggeri con 19 anni di comprovata affidabilità nella fabbricazione. Resistenti ad ambienti estremi per applicazioni aerospaziali, impianti medicali e dispositivi a semiconduttore.

Applicazioni di tendenza

Le nostre soluzioni di substrati di precisione Dal 2007 serviamo clienti globali nei settori dei semiconduttori e dell'elettronica con substrati IC personalizzati e PCBA completi chiavi in mano.

Hardware per semiconduttori e intelligenza artificiale: packaging CPU/GPU, acceleratori IA, moduli ad alta potenza di calcolo

5G e comunicazioni: chip per stazioni base, moduli RF, interconnessioni ad alta frequenza

Veicoli per l'automotive e le nuove energie: sensori ADAS, circuiti integrati di gestione dell'alimentazione per veicoli elettrici, controller per batterie

Elettronica medica: dispositivi impiantabili, chip per diagnostica per immagini, monitoraggio dei pazienti

Controllo aerospaziale e industriale: avionica, moduli satellitari, controllori di robot, sistemi energetici

Elettronica di consumo: smartphone, dispositivi indossabili, droni con packaging di chip avanzato

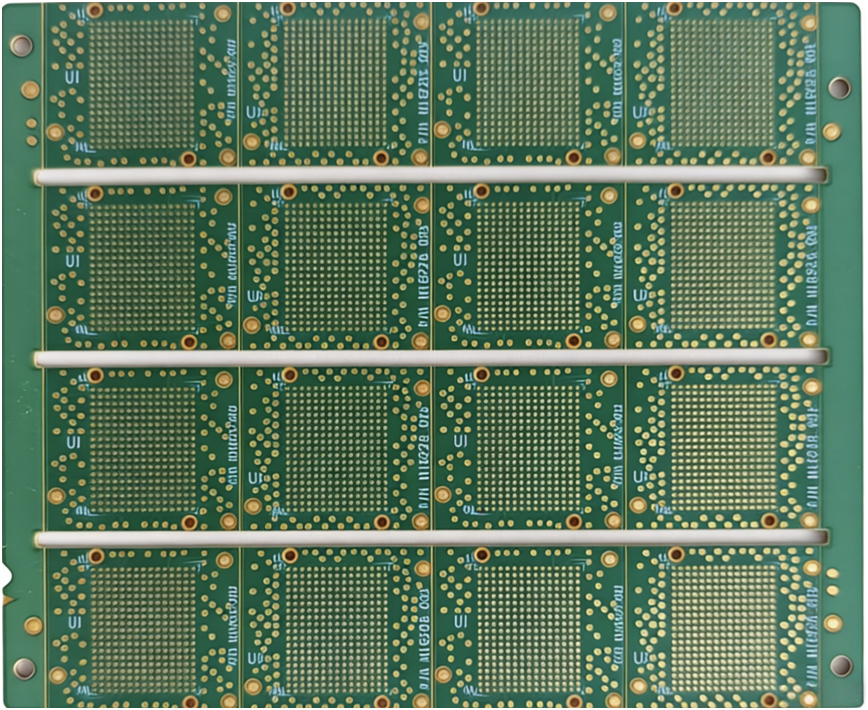

Capacità di produzione della nostra fabbrica

Shenzhen Benchuang Precision Electronics Co., Ltd. — Da 19 anni dedita alla produzione di substrati per PCB e circuiti integrati ad alta densità dal 2007. Attrezzature importate, progettazione interna completa e servizi PCBA completi.

Intervallo di 1-20 livelli

Traccia/spazio minimo 0,05 mm

Profili ultrasottili

Supporto Microvia e HDI

Materiali e processi

• Substrati FR-4 ad alta Tg / a bassa perdita / riempiti di ceramica

• Laminati in fogli di rame ricotto

• Progetti compatibili con HDI / RF / Rigid-Flex

• ENIG / OSP / Immersion Gold / Finiture superficiali avanzate

Dimensioni e tolleranze

• Dimensioni massime del pannello che supportano pacchetti IC complessi

• Tolleranza di spessore ±0,03 mm

• Maschera di saldatura e allineamento precisi per circuiti integrati a passo fine

• Opzioni di rinforzo e via termica

Capacità di servizio

• Prototipazione rapida in 24 ore per substrati IC

• Produzione da piccoli lotti a milioni di pezzi

• PCBA chiavi in mano in un unico punto: SMT + THT, BGA/QFN, AOI/ICT/test funzionali

• Revisione DFM completa, supporto al layout e logistica globale

Processo di produzione: dalla progettazione alla consegna in soli 7-15 giorni

01 Discussione sui requisiti - Conferma delle specifiche GERBER/IC

02 Prototipazione ingegneristica - Primo substrato in 48 ore

03 Validazione del campione - Test di segnale/termici/di affidabilità

04 Ottimizzazione della produzione di massa - Report DFM gratuito

05 Consegna puntuale - Monitoraggio logistico globale

Pronto a lanciare il tuo progetto di substrato per circuiti integrati?

Contattaci Email: william@bcpcbsz.com. I nostri tecnici risponderanno con un preventivo entro 2 ore (nei giorni feriali).