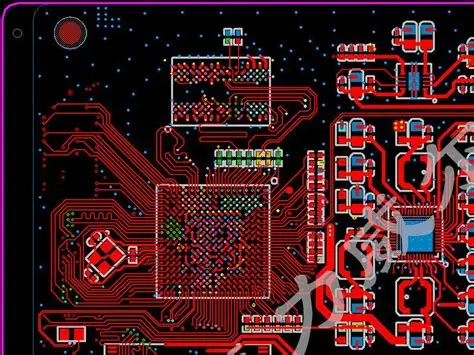

Lors de l'élaboration du circuit imprimé, comment garantir le bon fonctionnement de la mémoire flash et d'autres composants programmables ?

La programmation de la mémoire flash peut parfois prendre beaucoup de temps (jusqu'à une minute pour les mémoires de grande capacité ou les bancs de mémoire). Par conséquent, toute excitation inverse provenant d'autres composants doit être évitée pendant cette période, car elle pourrait endommager la mémoire flash. Pour ce faire, tous les composants connectés aux lignes de contrôle du bus d'adresse doivent être placés en haute impédance. De même, le bus de données doit pouvoir être isolé afin de garantir que la mémoire flash est déchargée et prête pour une programmation ultérieure.

Les composants programmables en système (ISP), tels que ceux d'Altera, Xilinx et Lattice, présentent des exigences spécifiques et d'autres particularités. Outre la vérification de leur testabilité mécanique et électrique, la capacité de programmation et de vérification des données doit être garantie. Pour les composants Altera et Xilinx, le format SVF (Serial Vector Format) est utilisé ; ce format est devenu une norme quasi-industrielle. De nombreux systèmes de test peuvent programmer ces dispositifs et utiliser les données d'entrée au format SVF pour générer les signaux de test.

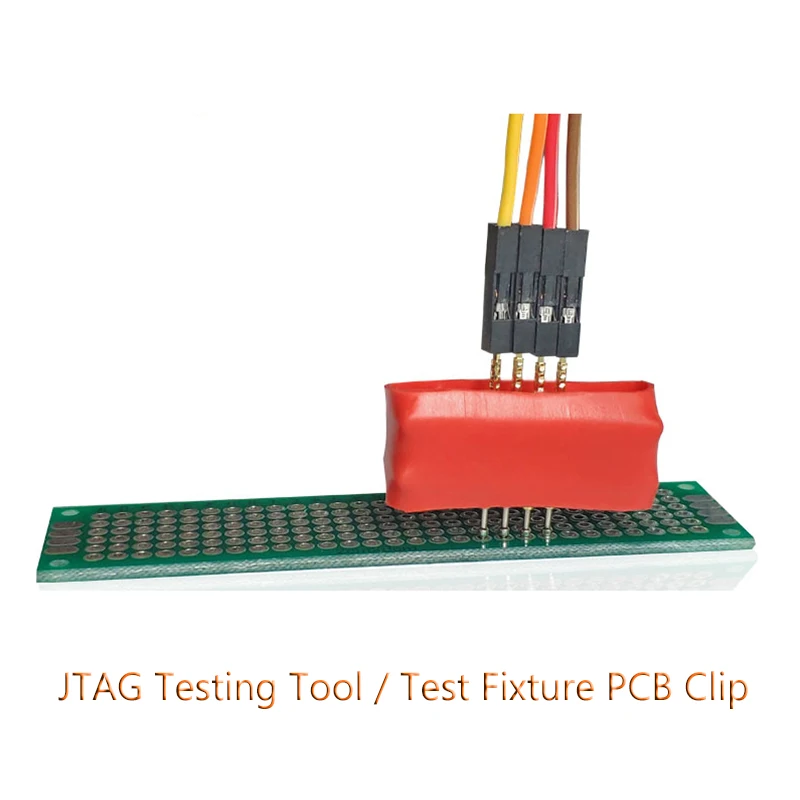

La programmation de ces dispositifs via la chaîne de balayage de limites (JTAG) utilise également le format de données série. Lors de la compilation des données de programmation, il est essentiel de prendre en compte l'ensemble de la chaîne de composants du circuit ; les données ne doivent pas se limiter au seul dispositif programmé. Pendant la programmation, le générateur de signaux de test automatisé prend en compte l'ensemble de la chaîne de composants et intègre les autres composants dans un modèle de contournement.

À l'inverse, Lattice requiert des données au format JEDEC et effectue une programmation parallèle via les ports d'entrée/sortie standard. Après la programmation, les données servent également à vérifier le bon fonctionnement des composants. Les données fournies par le service de développement doivent être utilisables directement par le système de test, ou après une conversion minimale.

Éléments à prendre en compte pour le balayage des limites (JTAG)

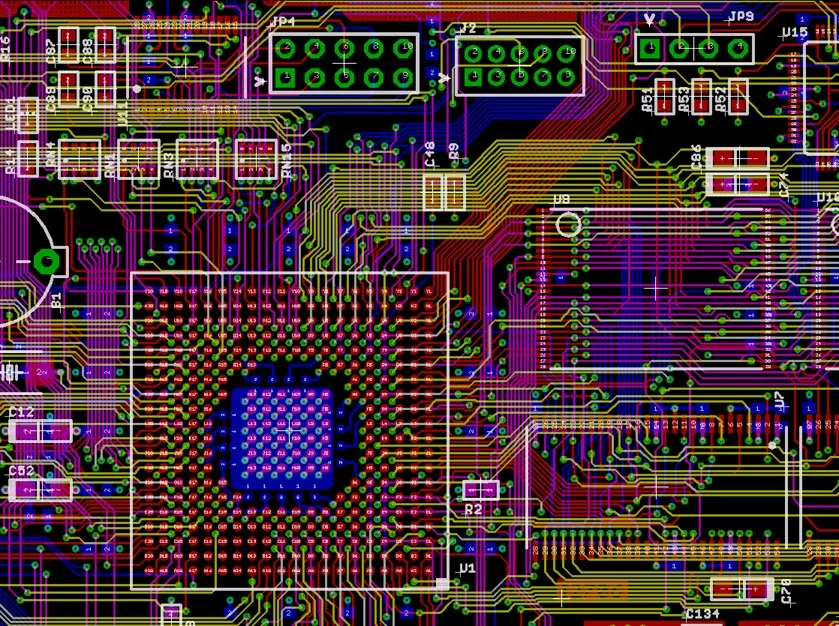

Les composants constitués de grilles complexes basées sur des éléments sophistiqués ne permettent aux ingénieurs de test qu'un nombre limité de points de test accessibles. Même dans ce cas, la testabilité peut être améliorée. Les technologies de balayage des limites et d'autotest intégré (IST) peuvent être utilisées pour réduire le temps d'exécution des tests et en améliorer l'efficacité.

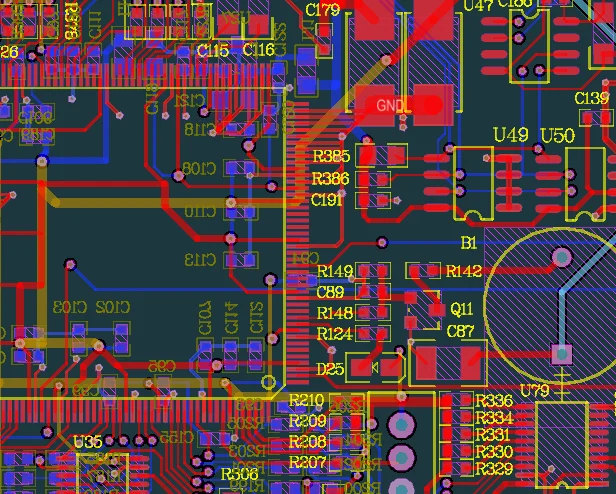

Pour les ingénieurs de développement et de test, la mise en place d'une stratégie de test basée sur les technologies de test aux limites et de test intégré (IST) entraîne inévitablement une augmentation des coûts. Les ingénieurs de développement doivent intégrer les composants de test aux limites (norme IEEE-1149.1) au circuit et s'assurer de l'accessibilité des broches de test spécifiques (par exemple, entrée de données de test - TDI, sortie de données de test - TDO, horloge de test - TCK, sélection du mode de test - TMS et éventuellement réinitialisation de test).

Les ingénieurs de test créent un modèle BSDL (Boundary Scan Description Language) pour le composant. À ce stade, ils doivent connaître les fonctions et commandes de test de limite prises en charge par le composant. Le test de limite permet de diagnostiquer les courts-circuits et les circuits ouverts jusqu'au niveau des pistes. De plus, si l'ingénieur de développement le spécifie, l'autotest intégré (BIST) du composant peut être déclenché par la commande de test de limite “ RunBIST ”. En particulier dans les circuits comportant de nombreux ASIC et autres composants complexes où les modèles de test conventionnels sont indisponibles, les composants de test de limite peuvent réduire considérablement le coût de développement de ces modèles.

L'ampleur des gains de temps et de coûts varie selon le composant. Pour un circuit contenant un circuit intégré nécessitant une couverture de défauts 100%, environ 400 000 vecteurs de test sont généralement nécessaires. Grâce au balayage de limites, ce nombre peut être réduit à quelques centaines tout en conservant le même taux de couverture de défauts. Par conséquent, cette approche présente des avantages indéniables lorsque les modèles de test sont indisponibles ou que l'accès aux nœuds du circuit est limité. Le choix du balayage de limites repose sur un équilibre entre l'augmentation des coûts lors du développement, de l'utilisation et de la fabrication. Il est essentiel de comparer le balayage de limites au temps de détection des défauts, au temps de test, au délai de mise sur le marché et aux coûts des adaptateurs, afin de maximiser les économies. Dans de nombreux cas, une approche hybride combinant les méthodes de test en circuit traditionnelles et le balayage de limites s'avère être la solution optimale.

Benchuang Electronics propose des produits de haute qualité Disposition du circuit imprimé et Circuit imprimé à grande vitesse services. Contactez-nous et envoyez-nous vos spécifications.