Diseñado para montaje directo de chips IC e interconexión de señales de alta velocidad. Admite de 1 a 20 capas con microvías y trazas/espacios finos de hasta 0,05 mm, perfiles ultrafinos y una disipación térmica excepcional. Del prototipo a la producción en masa en tan solo 7-15 días.

Ventajas principales

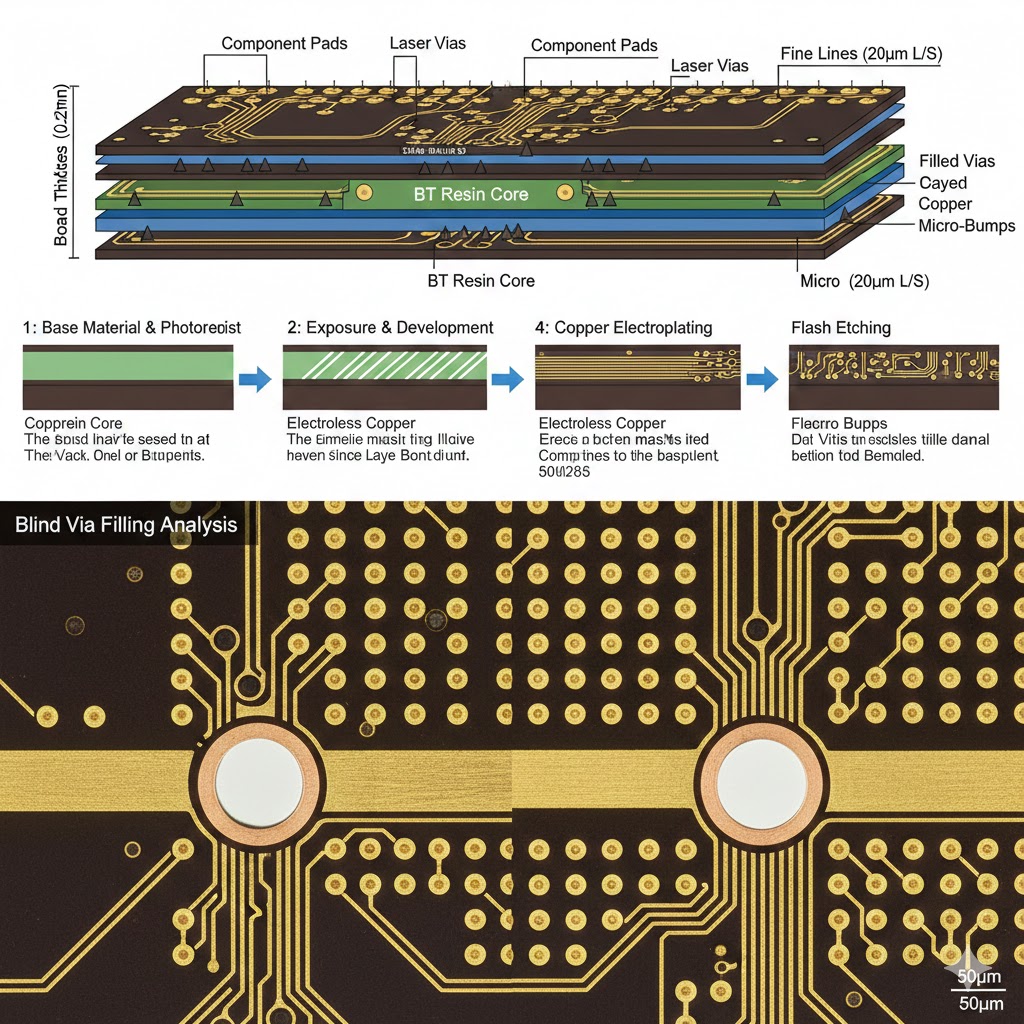

Densidad ultraalta y paso fino

Las microvías y trazas/espacios de hasta 0,05 mm permiten un enrutamiento complejo para el encapsulado avanzado de circuitos integrados. Puente perfecto entre el chip y la PCB principal para una integración máxima.

Integridad de señal superior y rendimiento de alta velocidad

Optimizado para aplicaciones de RF y alta frecuencia con materiales de baja pérdida: ideal para módulos 5G, procesadores de IA y computación de alto rendimiento.

Excelente gestión térmica

Los materiales y diseños avanzados disipan el calor de manera eficiente de los chips que consumen mucha energía, lo que garantiza la confiabilidad en ADAS automotrices, sistemas de baterías de vehículos eléctricos y equipos industriales.

Miniaturización y confiabilidad

Sustratos ultrafinos y ligeros con 19 años de experiencia comprobada en fabricación de alta fiabilidad. Resistentes a entornos extremos para la industria aeroespacial, implantes médicos y dispositivos semiconductores.

Aplicaciones de tendencia

Nuestras soluciones de sustrato de precisión Al servicio de clientes globales en semiconductores y electrónica desde 2007, ofrecemos sustratos de circuitos integrados (CI) personalizados y PCBA llave en mano completos.

Hardware de semiconductores e IA: empaquetado de CPU/GPU, aceleradores de IA, módulos de alto rendimiento

5G y comunicaciones: chips de estaciones base, módulos RF, interconexiones de alta frecuencia

Vehículos automotrices y de nuevas energías: sensores ADAS, circuitos integrados de gestión de energía para vehículos eléctricos, controladores de batería

Electrónica médica: dispositivos implantables, chips de diagnóstico por imágenes, monitorización de pacientes

Control aeroespacial e industrial: aviónica, módulos satelitales, controladores de robots, sistemas de energía

Electrónica de consumo: teléfonos inteligentes, wearables y drones con chips avanzados

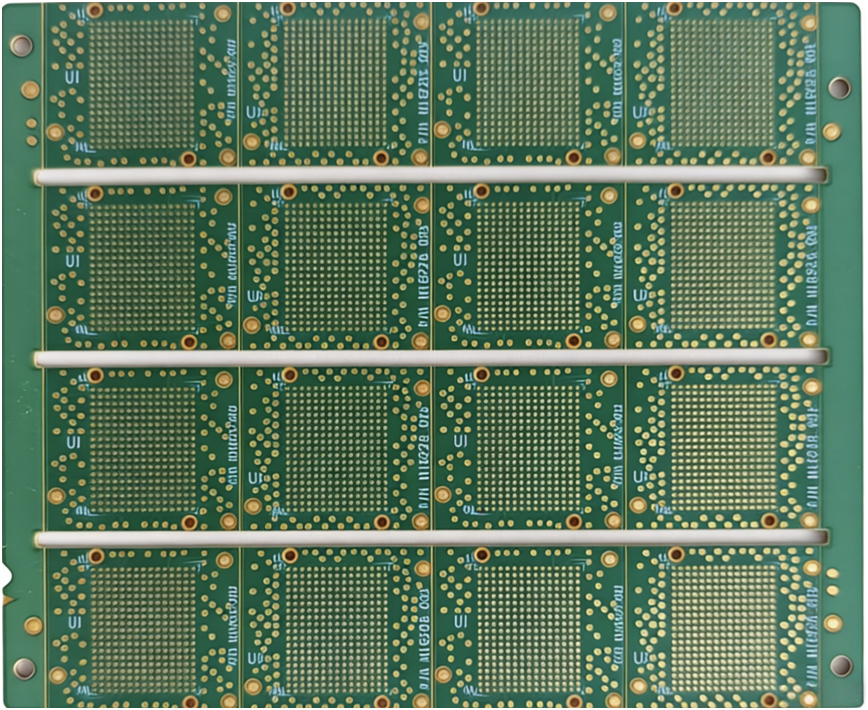

Capacidades de fabricación de nuestra fábrica

Shenzhen Benchuang Precision Electronics Co., Ltd.: 19 años dedicados a la fabricación de sustratos de PCB y IC de alta densidad desde 2007. Equipos importados, ingeniería interna completa y servicios de PCBA integrales.

Rango de 1 a 20 capas

Traza/espacio mínimo de 0,05 mm

Perfiles ultrafinos

Compatibilidad con Microvia y HDI

Materiales y procesos

• Sustratos FR-4 de alta Tg / baja pérdida / rellenos de cerámica

• Láminas de cobre recocido laminado

• Diseños compatibles con HDI/RF/Rígido-Flexible

• ENIG / OSP / Oro de inmersión / Acabados superficiales avanzados

Dimensiones y tolerancias

• Tamaño máximo de panel compatible con paquetes de circuitos integrados complejos

• Tolerancia de espesor ±0,03 mm

• Máscara de soldadura precisa y alineación para circuitos integrados de paso fino

• Opciones de refuerzo y vía térmica

Capacidades de servicio

• Prototipado rápido de sustratos de circuitos integrados en 24 horas

• Producción desde lotes pequeños hasta un millón

• PCBA llave en mano en un solo lugar: SMT + THT, BGA/QFN, AOI/ICT/Pruebas funcionales

• Revisión completa de DFM, soporte de diseño y logística global

Proceso de producción: desde el diseño hasta la entrega en tan solo 7-15 días

01 Discusión de requisitos - Confirmación de especificaciones GERBER/IC

02 Prototipado de Ingeniería - 48 Horas Primer Sustrato

03 Validación de muestra: pruebas de señal, térmicas y de confiabilidad

04 Optimización de la producción en masa - Informe DFM gratuito

05 Entrega a tiempo - Seguimiento logístico global

¿Está listo para lanzar su proyecto de sustrato IC?

Contáctenos Correo electrónico: william@bcpcbsz.com. Nuestros ingenieros le responderán con una cotización dentro de 2 horas (días laborables).