Um den durch die vorgenannten Maßnahmen hervorgerufenen Auswirkungen zu begegnen Probleme mit Übertragungsleitungen, Wir erörtern Methoden zur Kontrolle dieser Effekte aus folgenden Perspektiven.

1. Die Routinglänge kritischer Netzleitungen muss streng kontrolliert werden.

Bei Schaltungen mit schnellen Flankenübergängen müssen die Auswirkungen von Übertragungsleitungen auf der Leiterplatte berücksichtigt werden. Dieses Problem tritt besonders häufig bei modernen, hochfrequent getakteten integrierten Schaltungen auf. Grundlegende Prinzipien zur Behebung dieses Problems sind: – Bei CMOS- oder TTL-Schaltungen mit Betriebsfrequenzen unter 10 MHz sollte die Leiterbahnlänge 7 Zoll nicht überschreiten. – Bei Frequenzen bis 50 MHz sollte die Leiterbahnlänge 1,5 Zoll nicht überschreiten. – Bei Frequenzen ab 75 MHz sollte die Leiterbahnlänge auf 1 Zoll begrenzt werden. – Bei GaAs-Chips sollte die maximale Leiterbahnlänge 0,3 Zoll betragen. Eine Überschreitung dieser Grenzwerte führt zu Übertragungsleitungseffekten.

2. Rationale Planung der Leiterbahntopologie

Ein weiterer Ansatz zur Minderung von Übertragungsleitungseffekten besteht in der Auswahl geeigneter Leitungswege und Abschlusstopologien. Die Leiterbahntopologie beschreibt die Reihenfolge und den Aufbau der Verdrahtung eines Netzwerkkabels. Bei Verwendung von Hochgeschwindigkeitslogikbausteinen werden Signale mit schnell wechselnden Flanken durch Abzweigleitungen auf dem Hauptsignalstrang verzerrt, sofern die Abzweiglängen nicht extrem kurz gehalten werden. Typischerweise werden für die Leiterplattenverdrahtung zwei grundlegende Topologien verwendet: Reihenschaltung und Sternverdrahtung.

Bei der Daisy-Chain-Verdrahtung verlaufen die Leiterbahnen vom Treiber nacheinander zu jedem Empfänger. Werden Serienwiderstände zur Signalmodifikation eingesetzt, sollten diese direkt neben dem Treiber platziert werden. Die Daisy-Chain-Verdrahtung bietet die beste Leistung bei der Unterdrückung von Oberwellenstörungen auf den Leiterbahnen. Allerdings weist diese Verdrahtungsmethode die niedrigste Erfolgsrate auf und erreicht selten eine 100%-Verdrahtung. In der Praxis minimieren wir die Stichleitungslängen bei der Daisy-Chain-Verdrahtung. Ein sicherer Wert für die Stichleitungslänge ist: Stichleitungsverzögerung ≤ Trt * 0,1.

Beispielsweise sollten Stichleitungslängen in Hochgeschwindigkeits-TTL-Schaltungen weniger als 1,5 Zoll betragen. Diese Topologie benötigt minimalen Platz auf der Leiterbahn und kann mit einem einzigen Widerstand abgeschlossen werden. Allerdings führt diese Leiterbahnstruktur zu asynchronem Signalempfang an verschiedenen Signalempfängern.

Die Sterntopologie vermeidet effektiv Probleme mit der Taktsignal-Asynchronität, jedoch ist die manuelle Leiterbahnführung auf hochdichten Leiterplatten aufwendig. Der Einsatz eines automatischen Routers ist die beste Methode zur Sternverdrahtung. An jedem Zweig sind Abschlusswiderstände erforderlich. Der Widerstandswert des Abschlusswiderstands muss der Wellenimpedanz der Verbindung entsprechen. Dies kann manuell oder mithilfe von CAD-Tools berechnet werden, um die Wellenimpedanz und den passenden Widerstandswert zu ermitteln.

In den obigen Beispielen wurden zwar einfache Widerstände verwendet, komplexere Abschlussverfahren sind jedoch praktikable Alternativen. Die erste Möglichkeit ist der RC-Abschluss. Dieser reduziert den Stromverbrauch, eignet sich aber nur für stabile Signalbedingungen. Er ist besonders effektiv für die Taktleitungsanpassung. Ein Nachteil besteht darin, dass die Kapazität des RC-Abschlusses die Signalform und die Ausbreitungsgeschwindigkeit beeinflussen kann.

Der Abschlusswiderstand in Reihe verursacht keine zusätzlichen Leistungsverluste, verlangsamt jedoch die Signalausbreitung. Diese Methode wird in Bustreiberschaltungen eingesetzt, wo Zeitverzögerungen vernachlässigbar sind. Ein weiterer Vorteil des Abschlusswiderstands in Reihe ist die Möglichkeit, die Anzahl der Bauteile auf der Leiterplatte und die Verdrahtungsdichte zu reduzieren.

Die letzte Methode ist die diskrete Terminierung, bei der die passenden Bauteile in der Nähe des Empfängers platziert werden. Zu ihren Vorteilen zählen die Vermeidung von Signalabsenkungen und die effektive Rauschunterdrückung. Sie wird typischerweise für TTL-Eingangssignale (ACT, HCT, FAST) verwendet.

Zusätzlich müssen die Gehäuseart und die Ausrichtung des Abschlusswiderstands berücksichtigt werden. SMD-Oberflächenmontagewiderstände weisen im Allgemeinen eine geringere Induktivität als bedrahtete Bauteile auf, weshalb SMD-Gehäuse bevorzugt werden. Bei der Auswahl von Standard-Bedrahtungswiderständen stehen zwei Montageausrichtungen zur Verfügung: vertikal und horizontal.

Die vertikale Montage hält einen Anschluss kurz, wodurch der Wärmewiderstand zwischen Widerstand und Platine reduziert wird und die Wärme besser an die Umgebungsluft abgegeben werden kann. Allerdings erhöht eine höhere vertikale Montage die Induktivität des Widerstands. Die horizontale Montage bietet aufgrund ihrer geringeren Bauhöhe eine niedrigere Induktivität. Überhitzte Widerstände können jedoch driften und im schlimmsten Fall zu Unterbrechungen führen, was die Anschlussgenauigkeit der Leiterbahnen auf der Platine beeinträchtigt und somit einen potenziellen Fehlerfaktor darstellt.

3. Verfahren zur Unterdrückung elektromagnetischer Störungen

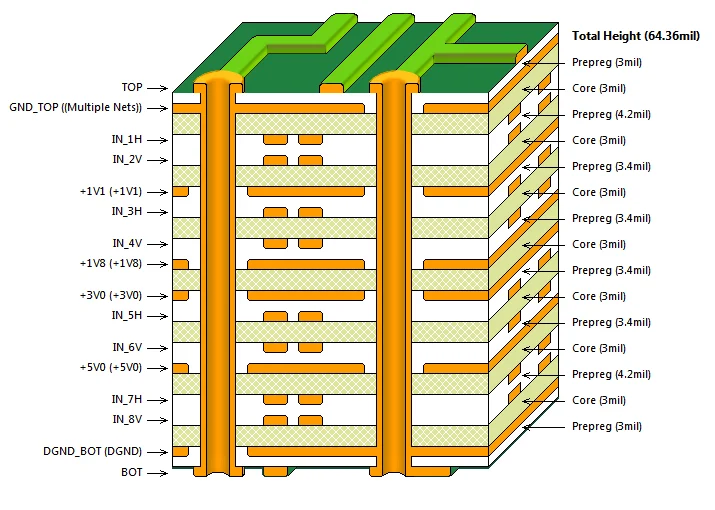

Die effektive Behebung von Signalintegritätsproblemen verbessert die elektromagnetische Verträglichkeit (EMV) von Leiterplatten. Eine ordnungsgemäße Erdung der Leiterplatte ist besonders wichtig. Bei komplexen Designs hat sich die Verwendung einer Signal- und einer Masseebene als äußerst effektiv erwiesen. Darüber hinaus ist die Minimierung der Signaldichte auf der äußersten Leiterplattenlage eine wirksame Methode zur Reduzierung elektromagnetischer Strahlung. Dies lässt sich durch Oberflächenstapelung (Surface Area Stacking, SAS) oder Aufbauverfahren für die Leiterplattenfertigung erreichen. SAS wird durch das Hinzufügen dünner Isolierschichten und Mikro-Vias realisiert, die diese Schichten auf einer Standard-Leiterplatte durchdringen. Widerstände und Kondensatoren können unter der Oberflächenlage eingebettet werden, wodurch sich die Leiterbahndichte pro Flächeneinheit nahezu verdoppelt und somit das Leiterplattenvolumen reduziert wird. Die Reduzierung der Leiterplattenfläche wirkt sich signifikant auf die Leiterbahntopologie aus, was zu kleineren Stromschleifen und kürzeren Verzweigungslängen führt. Da die elektromagnetische Strahlung annähernd proportional zur Fläche der Stromschleifen ist, ist diese Reduzierung vorteilhaft. Gleichzeitig ermöglicht die kompakte Bauform die Verwendung von Gehäusen mit hoher Pin-Dichte. Dies wiederum reduziert die Verbindungslängen, wodurch Stromschleifen weiter verkleinert und die elektromagnetische Verträglichkeit verbessert wird.

4. Weitere anwendbare Techniken

Um Spannungsspitzen in den Stromversorgungen integrierter Schaltungen (ICs) zu minimieren, sollten Entkopplungskondensatoren in die ICs integriert werden. Dies unterdrückt effektiv Störungen in der Stromversorgung und reduziert die Abstrahlung von Stromkreisen auf der Leiterplatte.

Entkopplungskondensatoren sorgen für eine optimale Glättung von Störimpulsen, wenn sie direkt an die Stromversorgungsanschlüsse des ICs anstatt an die Stromversorgungsebene angeschlossen werden. Dies erklärt, warum manche Gerätesockel Entkopplungskondensatoren enthalten, während andere erfordern, dass diese Kondensatoren äußerst nah am Gerät positioniert werden.

Alle Hochgeschwindigkeits- und Hochleistungskomponenten sollten so nah wie möglich beieinander platziert werden, um Spannungsspitzen in der Stromversorgung zu minimieren.

Ohne eine Stromversorgungsebene bilden lange Stromleitungen Schleifen zwischen Signal und Masse, die sowohl Strahlungsquellen als auch anfällige Schaltkreise darstellen.

Eine Leiterbahn, die eine Schleife bildet, ohne dasselbe Netz oder andere Leiterbahnen zu kreuzen, wird als offene Schleife bezeichnet. Kreuzt die Schleife andere Leiterbahnen im selben Netz, entsteht eine geschlossene Schleife. In beiden Fällen treten Antenneneffekte auf (Drahtantennen und Schleifenantennen). Antennen strahlen elektromagnetische Störungen (EMI) nach außen ab und fungieren gleichzeitig selbst als empfindliche Schaltungen. Geschlossene Schleifen sind besonders relevant, da ihre Abstrahlung annähernd proportional zur Schleifenfläche ist.

Abschluss

Die Entwicklung von Hochgeschwindigkeitsschaltungen ist ein äußerst komplexer Prozess. Die hier beschriebene Methodik befasst sich speziell mit diesen Herausforderungen. Darüber hinaus führen die zahlreichen Faktoren, die bei der Entwicklung von Hochgeschwindigkeitsschaltungen berücksichtigt werden müssen, häufig zu widersprüchlichen Prioritäten. Beispielsweise kann die enge Anordnung von Hochgeschwindigkeitskomponenten zwar die Verzögerung reduzieren, aber gleichzeitig Übersprechen und erhebliche thermische Effekte verursachen. Daher müssen bei Designentscheidungen diese Faktoren durch umfassende Abwägungen gegeneinander abgewogen werden – die Designanforderungen müssen erfüllt und gleichzeitig die Komplexität minimiert werden.

Benchuang Electronics bietet hochwertige PCB-Layout und Hochgeschwindigkeits-Leiterplatte Dienstleistungen. Nehmen Sie Kontakt mit uns auf und senden Sie uns Ihre Spezifikationen.